1. 개요

차량에서 처리하는 데이터가 많아지고 고속 통신을 요구하면서 차량 제어기에서 SoC 칩의 중요성이 커지고 있습니다.

최근 대부분의 SoC 칩은 CMOS 기술을 기반으로 설계되고 있는데, SoC 칩 설계에서 널리 사용되고 있는 이유는 다음과 같습니다.

첫째, 낮은 전력소비입니다. CMOS는 전류가 흐르지 않을 때 전력이 거의 소모되지 않아 대기상태에서 전력 소모를 최소화할 수 있습니다. 또한 CMOS 트랜지스터의 스위칭 활동 중에만 전력을 소모하므로, 효율적인 동적 전력 관리가 가능합니다.

둘째 전력 관리 측면입니다. CMOS 기반 SoC 칩은 여러 방식의 슬립모드를 지원하여 각 상황에 맞는 최적의 전력 소모를 구현할 수 있습니다. 또한 전력 게이팅/클럭 게이팅 기술을 사용하여 각 블록의 전력 소모를 세밀하게 조절할 수 있습니다.

셋째, 성능 향상 측면입니다. CMOS 기반 SoC칩은 빠른 스위칭 속도를 제공하여 메모리의 데이터 접근 속도를 향상시킵니다. 또한 캐시 메모리의 저장 및 검색 속도를 높여 데이터의 빠른 접근과 처리를 지원합니다.

2. SOC칩 메모리 계층 구조

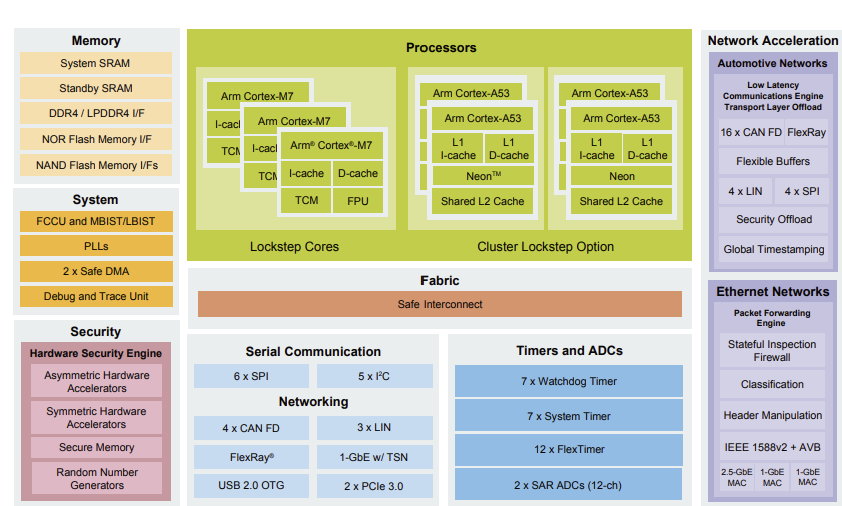

일반적으로 MCU칩은 소형 임베디드 시스템에 사용되며, SRAM/Flash메모리 등의 내장 메모리에서 대부분의 데이터를 처리합니다. SoC 칩은 고속 데이터처리, 고해상도 그래픽 통신 등의 다양한 어플리케이션을 지원해야하기 때문에 대량의 메모리와 고효율 저장공간이 필요합니다. 따라서 SoC 칩의 메모리 계층 구조는 내장 메모리뿐만 아니라 외장 메모리 인터페이스를 포함하며, 다양한 메모리 기술을 활용하여 성능과 효율성을 최적화합니다. 주요 메모리 요소로는 System SRAM, Standby SRAM, DDR 메모리, NAND Flash 등이 있습니다.

1) System SRAM

SoC 칩 내부에 위치하며, CPU나 Processor core와 가까운 곳에 배치됩니다. System SRAM은 매우 빠른 접근 속도를 제공하는 고속메모리로, CPU 캐시 메모리 등의 용도로 사용됩니다. 이는 실시간 게이트웨이 처리와 같이 자주 접근하거나, 고속 처리가 필요한 데이터를 저장하여 성능을 향상시킵니다. System SRAM은 휘발성 메모리로, 전원이 공급되는 동안만 데이터를 유지합니다.

2) Standby SRAM

Standby SRAM은 System SRAM과 유사하게 SoC 내부에 위치하나, 보통 System SRAM과는 구분되는 별도의 영역을 차지합니다. Standby SRAM은 저전력에서 동작하여 슬립모드와 같은 저전력 모드에서 활성상태를 유지하여 데이터를 보존할 수 있고 시스템이 재활성화될 때 신속하게 복구될 수 있습니다. 따라서 Standby SRAM은 저전력 모드에서 사용되어 전력을 효율적으로 사용하기 위해 활용할 수 있습니다.

3) DDR 메모리

SoC칩 외부에 위치하며 보통 메모리 모듈로 연결됩니다. DDR메모리는 대량의 데이터 저장에 사용되는 휘발성 메모리로 데이터가 전원이 공급되는 동안만 유지됩니다. 임베디드 칩에서 메인 시스템 메모리로 사용되며 높은 용량과 빠른 데이터 접근 속도를 제공하여 멀티태스킹과 대량 데이터 처리 작업에 활용될 수 있습니다. 한편, DDR메모리는 높은 대역폭과 빠른 접근 속도를 지원하지만 외부 메모리이기 때문에 CPU와 직접 연결된SRAM에 비해서는 처리 속도가 낮고, 초기화 시간이 오래걸립니다.

4) NAND Flash 메모리

SoC 외부에 위치하거나, SoC의 일부로 통합된 형태로 사용될 수 있습니다.

NAND Flash는 비휘발성 메모리로 전원이 꺼져도 데이터를 유지할 수 있습니다. 상태적으로 느리지만 대용량 데이터 저장이 가능하여 프로그램 코드, 내장스토리지, 데이터 기록 등에 사용됩니다.

3. Soc칩 메모리 계층 구조와의 상호작용

CMOS 기술은 빠른 스위칭 속도와 낮은 전력 소모를 제공합니다. 따라서 SRAM 캐시와 CPU간의 데이터 전송속도를 향상시켜 주며, 외부 메모리와 CPU 간의 데이터 전송을 보다 효율적으로 만들어 줍니다.

한편, SoC칩의 메모리 계층 구조는 각 메모리 구조와의 상호작용을 통해 데이터 접근을 최적화하였습니다.

외부 메모리에서 데이터가 요청될 때, SRAM 캐시는 자주 접근되는 데이터를 미리 저장해 두어, 다음 요청 시 더 빠르게 데이터를 제공할 수 있게 해줍니다. 만약 데이터가 캐시에 존재하지 않을 때는 외부메모리에서 데이터를 읽어옵니다.

SRAM의 캐시메모리는 이러한 방식으로 외부메모리와 CPU 간의 속도 차이를 줄이고 CPU가 자주사용하는 데이터를 빠르게 제공하여 전체 시스템의 성능을 향상시킵니다.

'차량 플랫폼' 카테고리의 다른 글

| 07 차량 플랫폼 - 차량용 SOC칩과 ARM core (0) | 2024.08.01 |

|---|---|

| 05. 차량 플랫폼 - MCU 프로그래밍 ISR (0) | 2024.06.13 |

| 04. 차량 플랫폼 - MCU 게이트웨이 기능과 메모리 (0) | 2024.06.06 |

| 03. 차량 플랫폼 - 이더넷 MCU (0) | 2024.06.06 |

| 02. 차량 플랫폼 - SOME/IP와 DDS의 차이 (2) | 2024.06.01 |